By Dr. Shu-Jen Han, CTO, SEEQC

As the field of quantum computing advances, one challenge that consistently stands at the forefront is scalability.

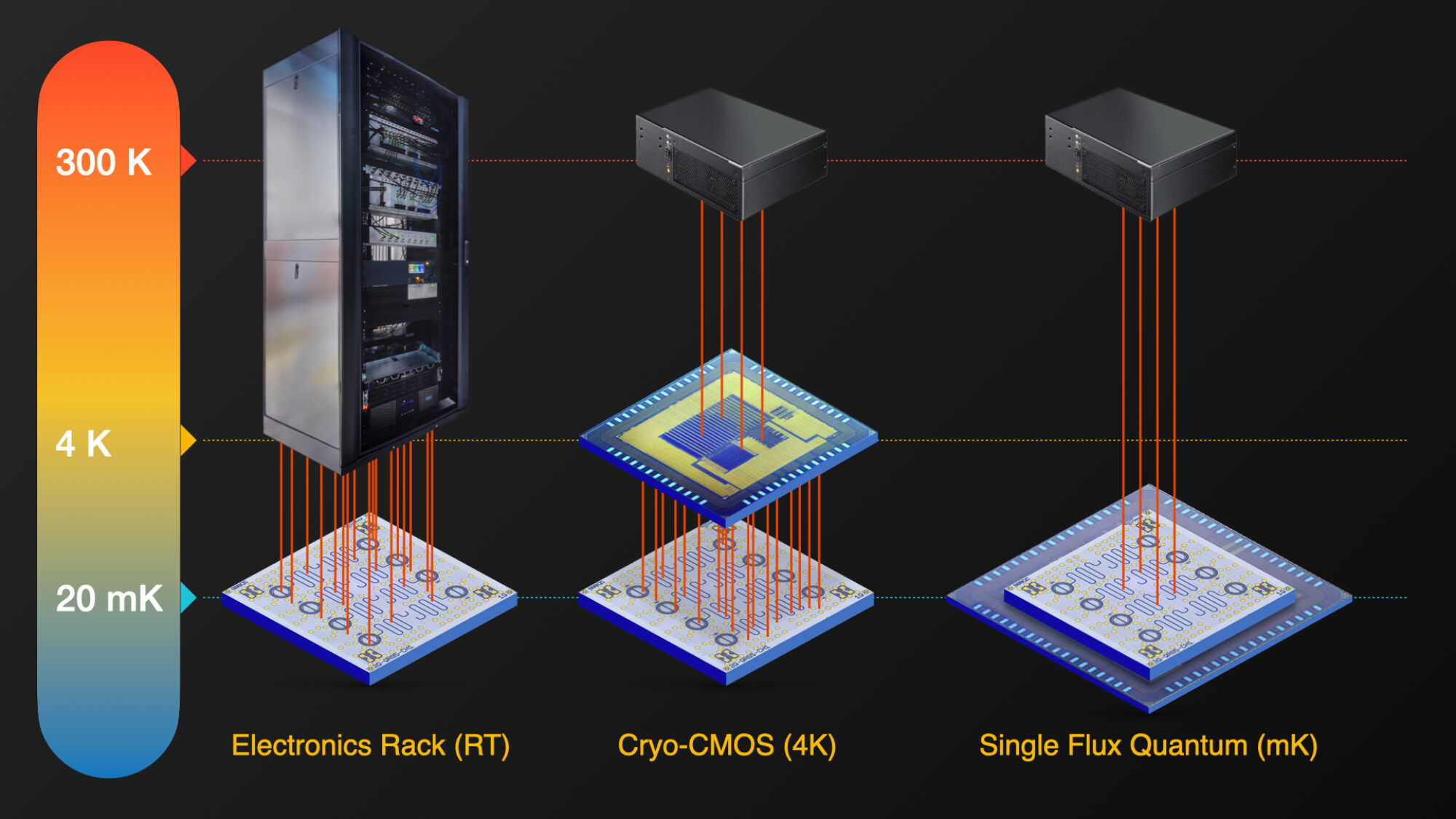

In light of these challenges, we are pleased to announce that SEEQC has made significant strides in addressing the scalability issue. This year at the APS March Meeting, we will showcase our groundbreaking chip solutions, which leverage a new approach to quantum electronics. Instead of using conventional CMOS, we employ Energy-efficient Rapid Single Flux Quantum (ERSFQ) logic technology. This cutting-edge approach drastically reduces power consumption—by orders of magnitude—enabling us to integrate qubits and their control and readout circuitry on the same chip.

This technology has the unique ability to operate at extremely low power levels, minimizing any adverse effects on qubit performance. By using ERSFQ logic, we are not only able to reduce power consumption, but also simplify the circuit complexity. This is a critical advancement, as the conventional microwave-based schemes used for quantum control are often bulky and power-hungry. Our novel digital scheme allows for more compact designs, which further reduce power consumption and enable smaller footprints for these circuits.

At this year’s APS March Meeting, we will be presenting a series of papers that demonstrate how these technological innovations are already laying the groundwork for the scalable quantum computers of the future. Our three presentations will highlight the key aspects of quantum computer operation:

1. High-Fidelity X/Y Control:

We will show how our technology enables high-fidelity qubit control with no observable quasiparticle positioning—a critical milestone in qubit stability and performance.

2. Two-Qubit Gate with Digital Flux Control:

Our approach to two-qubit gates, utilizing digital flux control, significantly reduces flux cross-talk, which is essential for ensuring the accuracy of quantum gates and minimizing error rates.

3. Compact On-Chip Digital Qubit Readout:

Leveraging our proprietary Josephson Digital Phase Detector (JDPD) technology, we present a compact, efficient solution for on-chip qubit readout, which is crucial for the scaling of quantum computers.

Additionally, we will demonstrate how these technologies integrate into a full-stack quantum computer, showcasing the potential for a new, scalable quantum architecture that can power the next generation of quantum computing systems.

For scientists and engineers striving to solve the quantum computer scaling problem, the work we are presenting at this year’s APS March Meeting marks a critical first step toward achieving a fully chip-based quantum solution. The integration of qubits with their control and readout electronics on the same chip—not only simplifies the system but also brings us closer to the practical realization of large-scale quantum computers. We believe this represents the future of quantum computing, one where performance and scalability are no longer at odds, but seamlessly integrated into a single, energy-efficient platform.

As we continue to make strides in developing scalable quantum computing systems, we invite others in the field to join us in this exciting journey. The path forward is clear: integrated chip solutions will be the key to unlocking the full potential of quantum computing. At SEEQC, we are proud to be at the forefront of this revolution, pioneering new technologies that will drive the future of quantum computing forward.

Join us at APS at the following sessions: